Digital Comprehensive Summaries of Uppsala Dissertations from the Faculty of Science and Technology 2520

# Advancements towards non-speculative concurrent execution of critical sections

EDUARDO JOSÉ GÓMEZ HERNÁNDEZ

ISSN 1651-6214 ISBN 978-91-513-2437-1 urn:nbn:se:uu:diva-552947

UPPSALA UNIVERSITET Dissertation presented at Uppsala University to be publicly examined in Salón de Grados, Facultad de Informatica (Building 32), University of Murcia, Murcia (Spain), Tuesday, 3 June 2025 at 16:00 for the degree of Doctor of Philosophy. The examination will be conducted in English. Faculty examiner: Professor Daniel Sorin (Duke University).

#### Abstract

Gómez Hernández, E. J. 2025. Advancements towards non-speculative concurrent execution of critical sections. (Avances hacia la ejecución concurrente y no especulativa de secciones críticas). *Digital Comprehensive Summaries of Uppsala Dissertations from the Faculty of Science and Technology* 2520. 74 pp. Uppsala: Acta Universitatis Upsaliensis. ISBN 978-91-513-2437-1.

Parallel programs require, besides the cache orchestration, another mechanism that guarantees synchronization among other threads of the same program. These synchronization mechanisms will induce overheads, by slowing down certain operations and stalling threads, among many others, to comply with the requirements established by the programmer.

The thesis's objective is the efficient execution of critical sections, that is, regions of code that must be executed atomically. The most efficient method is the concurrent and non-speculative executions of these sections. To achieve this, we present the 3 steps we have taken:1) single-atomic instructions can be used to implement non-speculative critical sections, therefore, we develop an updated version of the well-known Splash benchmark suite that uses single-address atomic instructions to implement most of the critical sections (Splash-4);2) a new set of multi-address atomic instructions, and a methodology on how to efficiently implement them, that can be used for small critical sections (MADs);3) without the direct intervention of the programmer, a more generic method that limits the retries required to execute contended critical regions (CLEAR).

For an efficient evaluation of the results, we have used the most up-to-date tools possible in each case, and even, when possible, real machines instead of simulations. For the simulations, we have used the gem5 simulator, at all times performing multiple runs. The simulator has been configured to emulate, as reliably as possible, processors based on the latest intel generations.

In our first step, Splash-4, we have managed to reduce the execution time by using 64cores by 50%, while maintaining the original structure and algorithms. In the second objective (MADs), the new atomic instructions implemented, reduce execution time by 80% compared to the classical lock mechanism, and by 60% by using a transitional memory technique similar to intel TSX, adding only 68 bytes per core. Finally, CLEAR is able to limit the number of re-executions of critical sections executed under speculative methods, increasing by 35% the number of sections that complete on the first retry, and reducing from 37% to 15% the number of sections that need to reach fallback. All this improving the execution time by 35% against an Intel TSX implementation and 23% against PowerTM.

*Keywords:* Computer Architecture, microarchitecture, atomic instructions, benchmark suite, non-speculative execution.

Eduardo José Gómez Hernández,

© Eduardo José Gómez Hernández 2025

ISSN 1651-6214 ISBN 978-91-513-2437-1 URN urn:nbn:se:uu:diva-552947 (http://urn.kb.se/resolve?urn=urn:nbn:se:uu:diva-552947)

To my family and friends

#### Acknowledgement

Developing a doctoral thesis is never an easy task. This is the conclusion, but also a new beginning, to my learning process. This challenge did not start 5 years ago, it started close to 8 years in the past. I had never anticipated that the number of life changes during this time would be that large. Like it is always said, "We walk on giant's shoulders". I would like to thank every person that has been there during these years.

First, to Raúl, my partner, my love. I found you when I was in my worst moments, I just exited several months of depression and some romantic issues. We have been distant friends for a long time ago, but we never connected that much. But, that day, in Barcelona, just for fun, it was the best day of my life. Since then, I trust you, I share all this with you. At the time of writing this thesis, we have been together for almost 3 years. I will save all the experiences we have been living during this time and the travels we have done in my heart forever. I love you. I just want to add, many thanks for teaming up with me in the biggest challenge of all, life.

To my parents (Isabel and Tomás) and my brother (Miguel). Things are hard, I know that my relationship with my brother is not as good as you always expected. I wanted to thank you for allowing me to do what I wanted to do, and to support me in the hard times. But most of all, thank you for accepting me like I am, with my oddities. Miguel, even if we have our differences, you also started a PhD after I started mine, and I hope things go well for you. Even after those fights we always have as brothers, many thanks for being there.

To my grandparents. You are no longer with us, but you have been very important in my life. Lelo, lela, thank you so much for teaching and caring about me all this time. Abuelo, abuela, even without being that close, you have been there, and I will always remember you. All of you have planted a seed in me and now it has bloomed. Many thanks for all of your time and effort. Just let me add, that I am very happy and very proud of being your grandson.

To my partner's parents and sister. Thank you so much for hosting me on those trips to Barcelona. We have also shared good and bad moments. It was great to see one of your dreams come true (your new house). Julia, I am so glad we were able to exchange books on every trip I made, it was great to have someone close that have similar reading interests. We need to make that reading club a reality.

To the rest of my family. You are a big family, I am not kidding, but even after those dad jokes that instead of breaking the ice, they froze the surrounding

air, you have been there. Usually to have a happy time. I remember very clearly those moments when you all met together, and because I was in Sweden, you sent me videos of you having fun, in part to encourage me to join you the next time. Thanks for being who you are.

To my "Morenos" and "TechCraft ESP" friends. This is a bit hard. I am sure that I would not be there if it were not for you. The day that a friend (Javi) told a teacher that I used to play chess, I met Radixan, my best friend, the first one to make a drastic change in my life. "TechCraft ESP" has influenced me so much, and I want to thank my friends Radixan and Jona for helping me there to build a dream. Also, I do not forget most of the players that have been around the server. "Morenos", the community where I met most of my friends. With special attention to Arekusanda, Sucraris (ArisNyan), and Anveloy. You are the best friends I have ever had. Also, Zoiris, thank you for sharing your time with me in those really bad moments I had. I want to give special thanks to Matu, Micki, Nil, and all the friends in the community that have been part of my life. To all of you, thanks.

To my World of Warcraft Guild friends (Ultimo Try - Tyrande). I am sorry that I left the game, and because of that, interacting with some of you has become a bit hard. But I want to say, thank you. From our mother, Ilmatar, to our breakable tank Akodo. Of course, I will never forget all those moments, all those raids, all those screams. Also, I keep a special space in my mind for Hati, Icelus, Blind, Eretikos, Kya, Kudo, Kysle, Mainal, Pelo, Volthum, and many more that have been coming and leaving on each big update. Thank you for supporting me, but also for all those nights stuck in the raid bosses, and mythic+.

To Jose Manuel García Carrasco, thanks to you, I am here. At the third of my bachelor's I was not expecting to be doing some research, I even had an offer to work with some friends on a topic I loved at the time. However, that email, after finishing AOC, and my first experience doing some research was the ignition spark of this engine. I know, for sure, that if it was not for that email, I would not be here right now.

To JuanMa, so many hours talking, discussing, and supporting each other. I remember very clearly that day that you went into the laboratory and told me about Alberto looking for me to work on the ECHO project. Not only that but working alongside you was a pleasure. You have taught me a lot of technical things. But technical discussions are not everything, you have taught me how to develop solutions, but also about life itself. Many thanks for all this time.

To my advisors Alberto and Stefanos. First of all, sorry for being so annoying, but many thanks for all the support you gave, and are still giving me. Those moments in Uppsala, the discussions on the whiteboard, that evening working in the HPCA PC meeting, and the messages we exchanged, of it are part of my precious memories that I will never forget. The only thing I regret was not using my time there in Uppsala better to learn much more from you. Alberto, you have introduced me to this lovely field, teaching me why most of my previous knowledge was wrong, teaching how this system works. Each discussion I had, and still have, with you is so fulfilling. Also, thank you so much for all those days we were able to talk outside the university and the academic field. Thank you so much.

To my colleagues at the University of Murcia: David, Paco, Ashkan, Sawan, Nikitin, Sebas, Agus, Nico, Pascual, Victor, Adrian, Ruben, Manolo, Ricardo, Juan Luis, Alexandra, and everyone in the department. Those stressful moments with David, those discussions and happy moments with Paco, those long discussions with Ashkan, those jokes with Sawan, those dad jokes with Agus, those HTM tantrums with Nikitin, there are so many more things that it would take pages to enumerate. I just want to say, thank you, everyone.

To my colleagues at the Uppsala Universitet: CH, Per, Chris, David, Gustaf, Anirban, Pavlos, Hassan, Oskar, Ali, Rashid, Ahmed, Shiming, Marina, Alireza, Johan, Yuan, and many more. Thank you for welcoming me and supporting me during the year I spent there. Working with you, going to midsommar, and living in Uppsala, has been a pleasure.

Paco, you have listened to me in the weak moments and given us a lot of support, many thanks for being there. Ester, you are not only a cleaner lady, but you are also a friend, I love those days talking, they have been very inspirational. The rest of the university staff, your support is invaluable.

To my students, I am not the best teacher, but it was special to see all of you growing up and where you are right now. I would like to mention Nico, Alvaro, and my 2024 SOEAR students (Pascual, Victor, Arturo, Adrian, and Emilio). Some of you are now colleagues, it was impressive to see how much you have learned and improved in these years, you have been part of keeping up this motivation engine we have inside. Now, most of you are teaching me new things.

To all of you, thank you very much for making all of this possible.

#### List of papers

This thesis is based on the following papers, which are referred to in the text by their Roman numerals.

- I Eduardo José Gómez-Hernández, Juan M. Cebrian, Stefanos Kaxiras, Alberto Ros, "Splash-4: A Modern Benchmark Suite with Lock-Free Constructs". 2022 IEEE International Symposium on Workload Characterization (IISWC 2022)

- II Eduardo José Gómez-Hernández, Juan M. Cebrian, Rubén Titos-Gil, Stefanos Kaxiras, Alberto Ros, "Efficient, Distributed, and Non-Speculative Multi-Address Atomic Operations". 54th Annual IEEE/ACM International Symposium on Microarchitecture (MICRO-54)

- III Eduardo José Gómez-Hernández, Juan M. Cebrian, Stefanos Kaxiras, Alberto Ros, "Bounding Speculative Execution of Atomic Regions to a Single Retry". International Conference on Architectural Support for Programming Languages and Operating Systems 2024 (ASPLOS 2024)

Reprints were made with permission from the publishers.

### Contents

| Ac | Acknowledgement                                                                                                                                                                                                                                                                                                                                                        | v                                                                                                        |  |

|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|--|

| 1  | Abstract                                                                                                                                                                                                                                                                                                                                                               |                                                                                                          |  |

| 2  | Sammanfattning                                                                                                                                                                                                                                                                                                                                                         |                                                                                                          |  |

| 3  | Resumen                                                                                                                                                                                                                                                                                                                                                                |                                                                                                          |  |

| 4  | Introduction                                                                                                                                                                                                                                                                                                                                                           |                                                                                                          |  |

| -  |                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                          |  |

|    |                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                          |  |

| 5  | Background                                                                                                                                                                                                                                                                                                                                                             |                                                                                                          |  |

|    | 5.1 Cache coherence                                                                                                                                                                                                                                                                                                                                                    |                                                                                                          |  |

|    | 5.2 Parallel benchmark suites                                                                                                                                                                                                                                                                                                                                          |                                                                                                          |  |

|    | 5.3 Synchronization primitives                                                                                                                                                                                                                                                                                                                                         |                                                                                                          |  |

|    |                                                                                                                                                                                                                                                                                                                                                                        | tructions                                                                                                |  |

|    |                                                                                                                                                                                                                                                                                                                                                                        | tions                                                                                                    |  |

|    | 5.6 Speculative execution of cri                                                                                                                                                                                                                                                                                                                                       | ical sections                                                                                            |  |

|    | 5.7 Non-speculative and concur                                                                                                                                                                                                                                                                                                                                         | rent execution                                                                                           |  |

|    |                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                          |  |

| 6  | Methodology                                                                                                                                                                                                                                                                                                                                                            |                                                                                                          |  |

| 6  |                                                                                                                                                                                                                                                                                                                                                                        | 43 43                                                                                                    |  |

| 6  | 6.1 Simulator                                                                                                                                                                                                                                                                                                                                                          |                                                                                                          |  |

| 6  | <ul><li>6.1 Simulator</li><li>6.2 Real Machine</li></ul>                                                                                                                                                                                                                                                                                                               |                                                                                                          |  |

| 6  | <ul><li>6.1 Simulator</li><li>6.2 Real Machine</li><li>6.3 Benchmarks</li></ul>                                                                                                                                                                                                                                                                                        |                                                                                                          |  |

| 6  | <ul><li>6.1 Simulator</li><li>6.2 Real Machine</li><li>6.3 Benchmarks</li><li>6.4 Methods</li></ul>                                                                                                                                                                                                                                                                    | 43<br>43<br>43<br>43                                                                                     |  |

| 6  | <ul> <li>6.1 Simulator</li> <li>6.2 Real Machine</li> <li>6.3 Benchmarks</li> <li>6.4 Methods</li> <li>6.5 Metrics</li> </ul>                                                                                                                                                                                                                                          | 43<br>43<br>43<br>43<br>43<br>45                                                                         |  |

|    | <ul> <li>6.1 Simulator</li> <li>6.2 Real Machine</li> <li>6.3 Benchmarks</li> <li>6.4 Methods</li> <li>6.5 Metrics</li> <li>Splash-4</li> </ul>                                                                                                                                                                                                                        | 43<br>43<br>43<br>43<br>45<br>45<br>45<br>47                                                             |  |

|    | <ul> <li>6.1 Simulator</li> <li>6.2 Real Machine</li> <li>6.3 Benchmarks</li> <li>6.4 Methods</li> <li>6.5 Metrics</li> <li>Splash-4</li> <li>7.1 Introduction</li> </ul>                                                                                                                                                                                              | 43<br>43<br>43<br>43<br>45<br>45                                                                         |  |

|    | <ul> <li>6.1 Simulator</li> <li>6.2 Real Machine</li> <li>6.3 Benchmarks</li> <li>6.4 Methods</li> <li>6.5 Metrics</li> <li>Splash-4</li> <li>7.1 Introduction</li> <li>7.2 Synchronization Issues</li> </ul>                                                                                                                                                          | 43<br>43<br>43<br>43<br>45<br>45<br>45<br>47<br>47                                                       |  |

|    | <ul> <li>6.1 Simulator</li> <li>6.2 Real Machine</li> <li>6.3 Benchmarks</li> <li>6.4 Methods</li> <li>6.5 Metrics</li> <li>Splash-4</li> <li>7.1 Introduction</li> <li>7.2 Synchronization Issues</li> <li>7.3 Efficient synchronization</li> </ul>                                                                                                                   | 43<br>43<br>43<br>43<br>45<br>45<br>45<br>45<br>47<br>47<br>47                                           |  |

|    | <ul> <li>6.1 Simulator</li> <li>6.2 Real Machine</li> <li>6.3 Benchmarks</li> <li>6.4 Methods</li> <li>6.5 Metrics</li> <li>Splash-4</li> <li>7.1 Introduction</li> <li>7.2 Synchronization Issues</li> <li>7.3 Efficient synchronization</li> <li>7.4 Results</li> </ul>                                                                                              | 43<br>43<br>43<br>43<br>45<br>45<br>45<br>45<br>47<br>47<br>47<br>47                                     |  |

| 7  | <ul> <li>6.1 Simulator</li> <li>6.2 Real Machine</li> <li>6.3 Benchmarks</li> <li>6.4 Methods</li> <li>6.5 Metrics</li> <li>Splash-4</li> <li>7.1 Introduction</li> <li>7.2 Synchronization Issues</li> <li>7.3 Efficient synchronization</li> <li>7.4 Results</li> <li>Hardware Multi-Address Atomics</li> </ul>                                                      | 43<br>43<br>43<br>45<br>45<br>45<br>47<br>47<br>47<br>47<br>47<br>51                                     |  |

| 7  | <ul> <li>6.1 Simulator</li> <li>6.2 Real Machine</li> <li>6.3 Benchmarks</li> <li>6.4 Methods</li> <li>6.5 Metrics</li> <li>Splash-4</li> <li>7.1 Introduction</li> <li>7.2 Synchronization Issues</li> <li>7.3 Efficient synchronization</li> <li>7.4 Results</li> <li>Hardware Multi-Address Atomics</li> <li>8.1 Introduction</li> </ul>                            | 43<br>43<br>43<br>43<br>45<br>45<br>45<br>47<br>47<br>47<br>47<br>47<br>47<br>51<br>54                   |  |

| 7  | <ul> <li>6.1 Simulator</li> <li>6.2 Real Machine</li> <li>6.3 Benchmarks</li> <li>6.4 Methods</li> <li>6.5 Metrics</li> <li>Splash-4</li> <li>7.1 Introduction</li> <li>7.2 Synchronization Issues</li> <li>7.3 Efficient synchronization</li> <li>7.4 Results</li> <li>Hardware Multi-Address Atomics</li> <li>8.1 Introduction</li> <li>8.2 Locking order</li> </ul> | 43<br>43<br>43<br>43<br>45<br>45<br>45<br>45<br>47<br>47<br>47<br>47<br>47<br>47<br>51<br>51<br>54<br>54 |  |

| 9  | cleA | R: Bounding TM to a single retry      | 63 |

|----|------|---------------------------------------|----|

|    | 9.1  | Introduction                          | 63 |

|    | 9.2  | High-contended immutable transactions | 63 |

|    | 9.3  | Bounding Retries                      | 64 |

|    | 9.4  | Results                               | 67 |

|    |      |                                       |    |

| 10 | Cond | clusion and Future Lines              | 69 |

| 10 |      | clusion and Future Lines              |    |

| 10 | 10.1 |                                       | 69 |

## List of Tables

| 6.1 | gem5 configuration                                                                                                            | 44 |

|-----|-------------------------------------------------------------------------------------------------------------------------------|----|

| 7.1 | Splash-3 Synchronization: 64 cores, default entries, each ex-                                                                 |    |

|     | ecution may vary the numbers a bit, numbers obtained with<br>our pin tool. St(atic) is the number of instances present in the |    |

|     | code, while Dyn(amic) is the number of instances executed in                                                                  |    |

|     | runtime.                                                                                                                      | 48 |

| 7.2 | Splash-4 Synchronization: 64 cores, default entries, each ex-                                                                 |    |

|     | ecution may vary the numbers a bit, numbers obtained with                                                                     |    |

|     | our pin tool. St(atic) is the number of instances present in the                                                              |    |

|     | code, while Dyn(amic) is the number of instances executed in                                                                  |    |

|     | runtime                                                                                                                       | 51 |

| 9.1 | Characterization of ARs                                                                                                       | 65 |

|     |                                                                                                                               |    |

## List of Figures

| 4.1        | A high-level graph of each contribution organized by papers.                             | 33       |

|------------|------------------------------------------------------------------------------------------|----------|

| 5.1        | High-level vision of a high-performance architecture with private and shared structures. | 36       |

| 5.2        | Mutex example                                                                            | 30       |

| 5.3        |                                                                                          | 39       |

| 5.5<br>7.1 | Barrier example                                                                          | 39       |

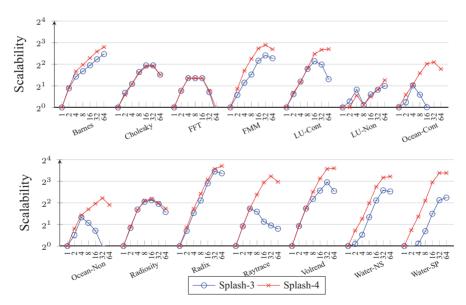

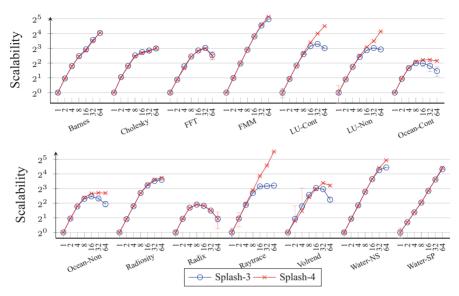

| /.1        | and both - <i>Splash-4</i> - (64-threads on AMD Epyc 7702P)                              | 52       |

| 7.2        | Splash-3 vs Splash-4 Scalability on AMD Epyc 7702P                                       | 52<br>52 |

| 7.2        |                                                                                          | 52       |

| 1.5        | Splash-3 vs Splash-4 Scalability in simulated Intel Ice Lake                             | 53       |

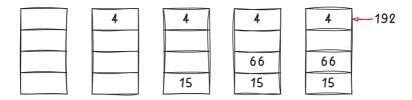

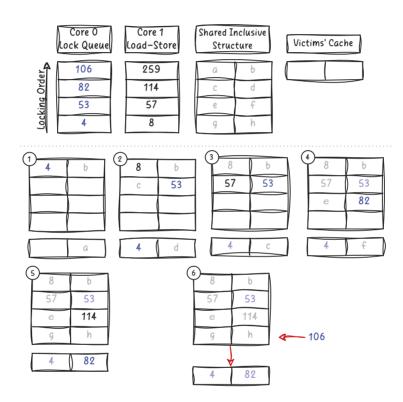

| 8.1        | (gem5-20)                                                                                | 55       |

| 0.1        | ing all addresses despite having enough space.                                           | 55       |

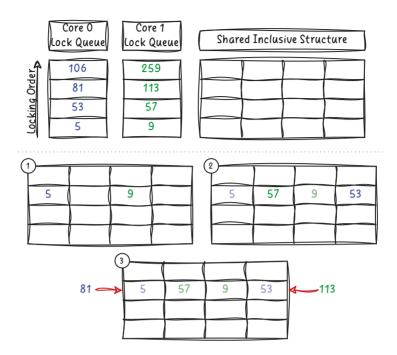

| 8.2        | Shared structure conflict because multiple cores lock addresses                          | 55       |

| 0.2        | in the same set of a shared inclusive structure.                                         | 56       |

| 8.3        | Deadlock scenario because the size limit of the MSHRs, caused                            | 50       |

| 0.5        | by a core that is not locking addresses                                                  | 57       |

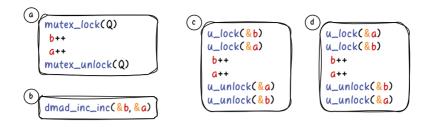

| 8.4        | a) Critical section with mutex locks; b) MAD atomic instruc-                             | 57       |

| 0.4        | tion; c) micro-ops generated by the MAD atomic; d) run-time                              |          |

|            | order of instructions                                                                    | 59       |

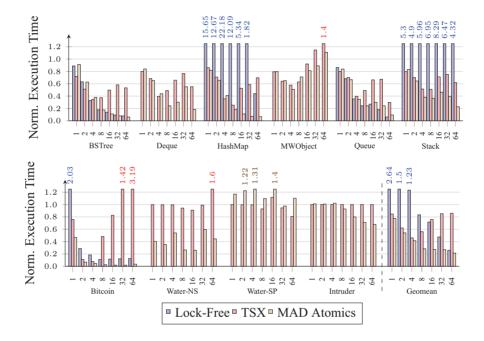

| 8.5        | Execution time (1 to 64 cores). Data is normalized to the lock                           | 39       |

| 0.3        | version with the same core count. Deque, MWObject, Bit-                                  |          |

|            | coin, Water-NS, and Water-SP do not have lock-free version.                              |          |

|            | Intruder does not have a lock or lock-free version, it is nor-                           |          |

|            | malized against TSX.                                                                     | 60       |

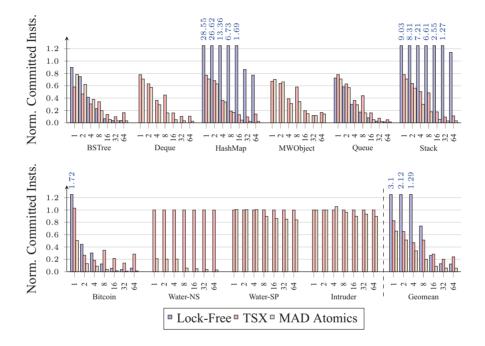

| 8.6        | Normalized committed instructions (1 to 64 cores). Data is                               | 00       |

| 0.0        | normalized against the lock version with the same core count.                            |          |

|            | Deque, MWObject, Bitcoin, Water-NS, and Water-SP do not                                  |          |

|            | have a lock-free version. Intruder does not have a lock or                               |          |

|            | lock-free version, it is normalized against TSX.                                         | 61       |

| 9.1        |                                                                                          | 01       |

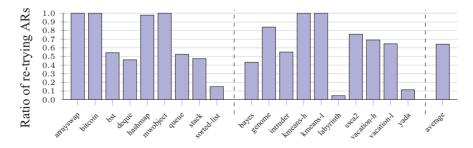

| 9.1        | ARs that do not change their accessed cachelines on the first                            | 63       |

| 0.2        | retry                                                                                    | 66       |

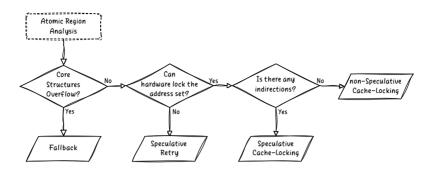

| 9.2<br>9.3 | Decision tree of the execution modes of cleAR                                            | 60<br>67 |

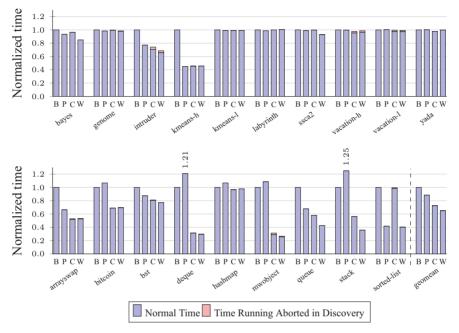

|            |                                                                                          | 67<br>68 |

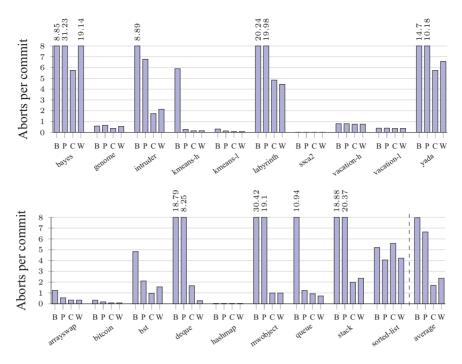

| 9.4        | Aborts per Committed Transaction                                                         | 08       |

## List of Listings

| 5.1 | Locking two variables                                      | 37 |

|-----|------------------------------------------------------------|----|

| 5.2 | Djistra locking                                            | 38 |

| 5.3 | While&CAS structure                                        | 39 |

| 7.1 | Sense-reversing barrier                                    | 48 |

| 7.2 | taskman.c.in 134                                           | 49 |

| 7.3 | multi.c.in 90                                              | 49 |

| 7.4 | interf.c.in 156 & interf.c.in 167 & interf.c.in 179        | 50 |

| 8.1 | Two-addresses fetch-and-add atomic operation in gem5-like  |    |

|     | micro-code                                                 | 58 |

| 9.1 | Inmutable AR. From arrayswap                               | 64 |

| 9.2 | Mutable AR. From sorted-list.                              | 65 |

| 9.3 | Conditionally Inmutable AR with indirections. From bitcoin | 65 |

#### 1. Abstract

Continuing the trend of increasing the performance of individual cores is no longer an easy task. During the last decades, manufacturers have moved the focus to adding multiple cores into the same chip (Chip-Multi-Processor or CMP). This paradigm change has allowed us to continue showing attractive performance improvements on each chip generation. On ideal conditions, an application should be able to increase its performance by a factor of the number of cores available in the chip, but several limitations will prevent the scalability of these applications.

CMPs are based on the Symmetric Multi-Processing model, where cores are identical and share the same unified memory space. However, the breach between memory and computing made each core require its own local highspeed memory, a cache. During the program's execution, each cache will start storing stale data, that is, data that no longer represents the actual expected value of a memory location. Cache coherence protocols eliminate this issue by orchestrating data movement between the memory and the caches. Despite the orchestration done by the coherence protocol, multiple threads may try to read and write into the same memory location (data race), producing an incorrect result.

Parallel programs require, besides the cache orchestration, another mechanism that guarantees synchronization among other threads of the same program. These synchronization mechanisms will induce overheads, by slowing down certain operations and stalling threads, among many others, to comply with the requirements established by the programmer.

A big issue when evaluating new proposals is the lack of comparison lines that are up-to-date and representative. The most used ones are benchmark suites, but most of them were crafted over 20 years ago. While some of them try to keep up with the architectural changes of the processors, many are left behind. One of the most misrepresented capabilities is the synchronization mechanisms.

The code regions that require synchronization are known as critical sections (or atomic regions). Depending on the nature and properties of these sections, different approaches can be used to protect them. Small ones with few addresses, "fine-grain", tend to be more efficient, but much harder to develop and debug; while big ones with several addresses, "coarse-grain", are trivial, even automatized, less prone to errors, but much less performant.

Different methods have been developed over the years to facilitate highperformance coarse-grain critical sections. Hardware Transactional Memory and Speculative Lock Elision are the most famous ones in this context. The main issue is that they introduce a lot of challenges to hardware designers while still showing doubts if they are a good approach.

The thesis's objective is the efficient execution of critical sections, that is, regions of code that must be executed atomically. The most efficient method is the concurrent and non-speculative executions of these sections. To achieve this, we present the 3 steps we have taken: 1) single-atomic instructions can be used to implement non-speculative critical sections, therefore, we develop an updated version of the well-known Splash benchmark suite that uses single-address atomic instructions to implement most of the critical sections; 2) a new set of multi-address atomic instructions, and a methodology on how to efficiently implement them, that can be used for small critical sections; 3) without the direct intervention of the programmer, a more generic method that limits the retries required to execute contended critical regions.

#### 2. Sammanfattning

Att fortsätta trenden med att öka prestandan hos enskilda kärnor är inte längre en lätt uppgift. Under de senaste decennierna har tillverkarna fokuserat på att lägga till flera kärnor på ett enda chip (Chip-Multi-Processor eller CMP). Detta paradigmskifte har gjort det möjligt att fortsätta att visa upp attraktiva prestandaförbättringar för varje generation av chip. Idealt sett borde en applikation kunna öka sina prestanda med en faktor som är lika med antalet tillgängliga kärnor på chipet, men det finns flera begränsningar som hindrar skalbarheten hos dessa applikationer.

CMP:er bygger på den symmetriska multiprocessmodellen, där kärnorna är identiska och delar samma enhetliga minnesutrymme. Gapet mellan minne och beräkning innebär dock att varje kärna behöver ett eget lokalt höghastighetsminne, en cache. Under exekveringen av ett program kommer varje cache att börja lagra gammal data, dvs data som inte längre representerar det faktiska värde som förväntas från en minnesplats. Protokoll för cachekoherens eliminerar detta problem genom att styra dataförflyttningen mellan minnet och cacheminnet. Trots den styrning som utförs av koherensprotokollet kan flera trådar försöka läsa och skriva till samma minnesplats (datarace), vilket ger ett felaktigt resultat.

Parallella program kräver, förutom cache-orkestrering, en annan mekanism för att säkerställa synkronisering mellan andra trådar i samma program. Dessa synkroniseringsmekanismer kommer att medföra omkostnader genom att bromsa vissa operationer, stoppa trådar och mycket annat för att uppfylla de krav som programmeraren har ställt.

Ett stort problem vid utvärderingen av nya förslag är bristen på aktuella och representativa benchmarks. De mest använda är benchmark-sviter (eller testsviter), men de flesta av dem skapades för mer än 20 år sedan. Även om vissa av dem försöker hålla jämna steg med processorarkitekturens förändringar, släpar många efter. Det finns några testsviter som hänger med i tiden och som till och med är prestandanormerande för dagens kommersiella processorer. Problemet med dessa moderna testsviter är exekveringstiden. Simulatorerna, med optimeringar, kan simulera några sekunders simulering efter flera timmar. Det är inte möjligt att köra de modernaste uppsättningarna på dem, vilket tvingar fram alternativa och oftast föråldrade testsviter. En av de mest felaktigt presenterade funktionerna är dock de tidigare nämnda synkroniseringsmekanismerna.

De delar av koden som kräver synkronisering kallas kritiska avsnitt (eller atomregioner). Beroende på hur dessa sektioner ser ut och vilka egenskaper de har kan olika metoder användas för att skydda dem. Små med få adresser, finkorniga, tenderar att vara effektivare, men mycket svårare att utveckla och felsöka; medan stora med flera adresser, grovkorniga, är triviala, till och med automatiserade, mindre felbenägna, men till priset av lägre prestanda. Det är välkänt att atomiska instruktioner med en enda adress är det mest effektiva sättet att utföra en uppdatering atomiskt i förhållande till resten av applikationstrådarna, eftersom de utför denna synkronisering via hårdvara. Många programmerare har dock valt att använda lås i kritiska avsnitt eftersom de är lätta att programmera.

Under årens lopp har olika metoder utvecklats för att underlätta grova kritiska sektioner med hög genomströmning. Syftet har varit att delegera till hårdvaran att fatta bästa möjliga beslut i varje givet ögonblick. I många fall är tanken att man inte ska behöva vara inlåst, utan fortsätta framåt, och i de fall där atomicitet inte kan garanteras, ångra ändringarna och försöka igen. Transaktionsminne i hårdvara och spekulativ låsning är de mest kända i det här sammanhanget. Huvudproblemet är att de medför många utmaningar för hårdvarukonstruktörer, samtidigt som det fortfarande råder tvivel om huruvida de är en bra metod.

Syftet med avhandlingen är att på ett effektivt sätt exekvera kritiska avsnitt, dvs. områden i koden som måste exekveras atomiskt. Den mest effektiva metoden är samtidig och icke-spekulativ exekvering av dessa avsnitt. För att uppnå detta presenterar vi de tre steg vi har tagit: 1) enkla atomära instruktioner kan användas för att implementera icke-spekulativa kritiska avsnitt, så vi utvecklade en uppdaterad version av den välkända Splash-testsviten som använder atomära instruktioner med en adress för att implementera de flesta av de kritiska avsnitten; 2) en ny uppsättning atomära instruktioner med flera riktningar, och en metod för hur man implementerar dem effektivt, som kan användas för små kritiska sektioner; 3) utan direkt inblandning av programmeraren, en mer generisk metod som begränsar antalet försök som krävs för att exekvera begränsade kritiska områden.

För en effektiv utvärdering av resultaten har vi använt de mest aktuella verktygen i varje enskilt fall och även, när det varit möjligt, riktiga maskiner i stället för simuleringar. För simuleringarna har vi använt gem5-simulatorn och hela tiden utfört flera körningar och validerat de erhållna resultaten. Simulatorn har konfigurerats för att så tillförlitligt som möjligt emulera processorer baserade på de senaste intel-generationerna.

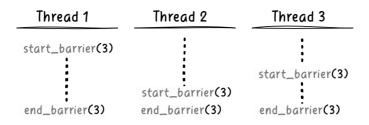

Splash-4, den nya versionen av Splash testsvit som vi har utvecklat under detta examensarbete, ersätter en betydande del av de kritiska sektioner som implementerats med hjälp av olika typer av konstruktioner. Dessa konstruktioner, som använder instruktioner med en adress, kan uttrycka högnivåoperationer som: "Om x är mindre än det värde som lagras på adress y, skriv x på adress y". Dessutom har vi inkluderat konstruktioner som implementerar befintliga operationer i andra atomics, men för datatyper som inte stöds, till exempel "atomically add x and what is stored at address y, and write the result to y" men för flyttal. Vi har stött på två exceptionella situationer: i den ena har vi delat upp en kritisk sektion i flera enkelriktade sektioner; i den andra har vi med hjälp av en konstruktion inom en konstruktion lyckats implementera en dubbelriktad kritisk sektion med hjälp av enkelriktade atomics. Kritiska sektioner är dock inte allt, det finns andra synkroniseringsprimitiver, t.ex. barriärer, som vi också har ersatt med alternativ som använder atominstruktioner med en adress för att minska overhead för en sådan primitiv. Denna overhead var särskilt viktig, eftersom det arbete som ska utföras mellan barriär och barriär är så litet på moderna processorer att exekveringstiden i vissa applikationer helt dominerades av väntan på andra trådar.

På grund av de stora begränsningarna hos atomära instruktioner med en adress har utvecklare i många år velat ha atomära instruktioner med flera adresser. Denna typ av instruktioner skulle göra det möjligt att implementera mer komplexa kritiska sektioner med samma effektivitet som atomiska instruktioner med en adress, med tanke på att atomiska instruktioner är det mest effektiva sättet att utföra en uppdatering i en riktning atomiskt i förhållande till resten av applikationens trådar. Detta är dock inte en enkel uppgift. När vi vill låsa flera minnesadresser måste vi vara extremt försiktiga så att vi inte hamnar i deadlocks där exekveringen inte kan fortsätta, till exempel tråd 1 har låst "x" och vill låsa "y", medan tråd 2 har låst "y" och vill låsa "x". För att lösa detta är den enklaste lösningen att använda en global ordning som alla följer: För att låsa "x" och "y", lås först "x" och sedan "y". Den här lösningen fungerar utmärkt i programvara, där resurserna antas vara tillräckliga (om än inte obegränsade). Atomiska instruktioner implementerar dock vanligtvis sina lås på cacheminnet, en fysisk struktur med ändliga och välbegränsade resurser.

Hur kan vi implementera atomära instruktioner med flera adresser om vi har begränsade resurser? Svaret vi föreslår är att vi tar hänsyn till dessa begränsningar när vi ordnar adresserna som ska blockeras. Genom att följa en serie mycket specifika steg när vi utför en låsning, och använda den lexikografiska ordningen på adresserna med hänsyn till storleken på den privata cachen, har vi lyckats låsa upp till 4 adresser samtidigt. Med hjälp av den här metoden har vi implementerat flera olika typer av atomära adressinstruktioner, inklusive den välkända compare-and-swap.

Trots genombrottet för atomära instruktioner med flera adresser är det fortfarande en stor utmaning att realisera komplexa algoritmer med dem. En av de största begränsningarna, förutom antalet adresser, är att de adresser som används är föränderliga. Atomiska instruktioner med en eller flera adresser kräver att de minnesadresser som ska låsas är kända i förväg och inte kan ändras. En kritisk sektion är inte föränderlig om de adresser som används, både vid läsning och skrivning, alltid är desamma när den exekveras flera gånger med samma processorregister. Med andra ord är minnesadresserna inte beroende av andra minnesadresser.

Det skulle vara mycket enklare om maskinvaran själv kunde hitta dessa adresser, bestämma mutabiliteten i den kritiska sektionen och utföra låsningen i rätt ordning utan att programmeraren behöver planera den kritiska sektionen och därmed bara markera början och slutet på den kritiska sektionen. De två mekanismer som befriar programmeraren från att definiera vilken typ av låsning som ska utföras och lämnar den uppgiften till maskinvaran själv är transaktionsminne i maskinvaran och undvikande av spekulativa deadlocks. Båda förslagen uppnår vad de föresatt sig att göra - programmeraren bestämmer bara kodregionerna och hårdvaran tar hand om att försöka exekvera dem så effektivt som möjligt. Ingen av metoderna är dock garanterad att göra framsteg, vilket innebär att de kan misslyckas och måste prövas på nytt om atomiciteten bryter samman. I båda situationerna är den vanligaste lösningen en alternativ exekveringsväg som förvärvar ett block (eller en latch) som tvingar fram atomicitet, på bekostnad av prestanda.

Men tänk om vi kunde dra nytta av dessa omförsök och låsa de nödvändiga minnesadresserna för att säkerställa att exekveringen slutförs framgångsrikt utan risk för konflikter? cleAR använder den första exekveringen för att analysera det kritiska avsnittet, få alla minnesadresser och även analysera beroendena för att välja den optimala exekveringsmetoden för att begränsa antalet omförsök som behövs till 1. När det kritiska avsnittet väl är i körning släpper cleAR på konfliktförebyggande mekanismen för att få så mycket information som möjligt från den första körningen. Om exekveringen avslutas med en konflikt väljer cleAR mellan följande tre alternativ: 1) blockera alla adresser och utföra en icke-spekulativ exekvering; 2) blockera en del av adresserna och utföra en spekulativ exekvering; och 3) blockera ingenting och fortsätta med basmekanismen. Om alternativ 1 väljs begränsas antalet omförsök till 1 och det finns ingen ytterligare risk för konflikter. Om den kritiska sektionen inte uppfyller alla krav för alternativ 1 kan vi ändå öka chanserna till framsteg genom att blockera de adresser som är benägna att orsaka konflikter (alternativ 2). Som ett sista alternativ kommer cleAR att delegera till den spekulativa mekanism som används för att hantera de kritiska avsnitt där den inte kan tillämpa någon av ovanstående mekanismer.

I vårt första steg, Splash-4, har vi lyckats minska exekveringstiden genom att använda 64 kärnor med 50%, samtidigt som vi behållit den ursprungliga strukturen och algoritmerna. I det andra målet (MADs) minskar de nya atomära instruktionerna exekveringstiden med 80% jämfört med den klassiska låsmekanismen och med 60% när man använder en teknik för övergångsminne som liknar intel TSX och bara lägger till 68 byte per kärna. Slutligen kan cleAR begränsa antalet omkörningar av kritiska avsnitt som exekveras med spekulativa metoder, öka antalet avsnitt som slutförs vid första omkörningen med 35% och minska antalet avsnitt som måste nå fallback från 37% till 15%. Allt detta förbättrade exekveringstiden med 35% jämfört med en Intel TSX-liknande implementation och 23% jämfört med PowerTM.

#### 3. Resumen

Continuar la tendencia de aumentar el rendimiento de los núcleos individuales ya no es tarea fácil. En las últimas décadas, los fabricantes se han centrado en añadir varios núcleos a un mismo chip (Chip-Multi-Processor o CMP). Este cambio de paradigma ha permitido seguir mostrando atractivas mejoras de rendimiento en cada generación de chips. En condiciones ideales, una aplicación debería poder aumentar su rendimiento en un factor equivalente al número de núcleos disponibles en el chip, pero existen varias limitaciones que impedirán la escalabilidad de estas aplicaciones.

Los CMP se basan en el modelo de multiprocesamiento simétrico, en el que los núcleos son idénticos y comparten el mismo espacio de memoria unificado. Sin embargo, la brecha entre memoria y computación hace que cada núcleo necesite su propia memoria local de alta velocidad, una caché. Durante la ejecución de un programa, cada caché empezará a almacenar datos obsoletos, es decir, datos que ya no representan el valor real esperado de una ubicación de memoria. Los protocolos de coherencia de caché eliminan este problema orquestando el movimiento de datos entre la memoria y las cachés. A pesar de la orquestación realizada por el protocolo de coherencia, varios hilos pueden intentar leer y escribir en la misma posición de memoria (carrera de datos), produciendo un resultado incorrecto.

Los programas paralelos requieren, además de la orquestación de la caché, otro mecanismo que garantice la sincronización entre otros hilos del mismo programa. Estos mecanismos de sincronización inducirán sobrecargas, al ralentizar ciertas operaciones, detener hilos, entre muchos otros, para cumplir con los requisitos establecidos por el programador.

Un gran problema a la hora de evaluar nuevas propuestas es la falta de líneas de comparación actualizadas y representativas. La más utilizada son las suites de benchmarks (o conjunto de pruebas), pero la mayoría de ellas fueron creadas hace más de 20 años. Aunque algunas de ellas intentan mantenerse al día con los cambios arquitectónicos de los procesadores, muchas se quedan atrás. Existen alunos conjuntos de pruebas que se mantienen al día, e incluso son los referentes del rendimiento en los procesadores comerciales actuales. El problema de estos conjuntos modernos es el tiempo de ejecución. Los simuladores, con optimizaciones puedes llegar a simular unos pocos segundos de simulación tras varias horas. Resulta inviable ejecutar los conjuntos más modernos en ellos, forzando al uso de conjuntos de pruebas alternativos, y mayormente desactualizados. Aún, así, una de las capacidades más tergiversadas son, los ya mencionados, mecanismos de sincronización. Las regiones de código que requieren sincronización se conocen como secciones críticas (o regiones atómicas). Dependiendo de la naturaleza y propiedades de estas secciones, se pueden utilizar diferentes enfoques para protegerlas. Las pequeñas con pocas direcciones, grano fino, tienden a ser más eficientes, pero mucho más difíciles de desarrollar y depurar; mientras que las grandes con varias direcciones, grano grueso, son triviales, incluso automatizadas, menos propensas a errores, pero a costa de un menor rendimiento. Es bien conocido que las instrucciones atómicas de dirección única son las manera más eficiente de realizar una actualización atómicamente respecto al resto de hilos de la aplicación, ya que realizan esta sincronización por hardware. Sin embargo, muchos programadores han optado por la secciones críticas usando bloqueos por su sencillez a la hora de programar.

A lo largo de los años se han desarrollado diferentes métodos para facilitar las secciones críticas de grano grueso de alto rendimiento. El objetivo era delegar en el hardware para que tomase la decisión más acertada posible en cada momento. En muchos casos la idea es no tomar ningún bloqueo, continuar hacia delante, y en el caso de que no se pueda garantizar la atomicidad, deshacer los cambios y volver a intentar. La memoria transaccional por hardware y la elisión especulativa de bloqueos son los más conocidos en este contexto. El principal problema es que introducen muchos retos para los diseñadores de hardware, al tiempo que siguen mostrando dudas sobre si son un buen enfoque.

El objetivo de la tesis es la ejecución eficiente de secciones críticas, es decir, regiones de código que deben ejecutarse atómicamente. El método más eficiente es la ejecución concurrente y no especulativa de estas secciones. Para lograrlo, presentamos los 3 pasos que hemos dado: 1) se pueden utilizar instrucciones atómicas simples para implementar secciones críticas no especulativas, por lo que desarrollamos una versión actualizada del conocido conjunto de pruebas Splash que utiliza instrucciones atómicas de dirección única para implementar la mayoría de las secciones críticas; 2) un nuevo conjunto de instrucciones atómicas multiple dirección, y una metodología sobre cómo implementarlas eficientemente, que pueden utilizarse para secciones críticas pequeñas; 3) sin intervención directa del programador, un método más genérico que limita los reintentos necesarios para ejecutar regiones críticas contendidas.

Para una eficiente evaluación de los resultados, hemos utilizado las herramientas mas actualizadas que nos han sido posibles en cada caso, e incluso, cuando ha sido posible, máquinas reales en lugar de simulaciones. Para las simulaciones, hemos usado el simulador gem5, en todo momento realizando multiples ejecuciones, y validando los resultados obtenidos. El simulador ha sido configurado para emular, lo más fiablemente posible, procesadores basados en las últimas generaciones de intel.

Splash-4, la nueva versión del conjunto de pruebas Splash que hemos desarrollado durante esta tesis, reemplaza una parte significativa secciones criticas implementadas usando distintos tipos de constructos. Estos constructos, usando instrucciones de dirección única, son capaces de expresar operaciones de

alto nivel como: "atómicamente si x es menor que el valor almacenado en la dirección y, escribe x en la dirección y". Adicionalmente, hemos incluido constructos que implementan operaciones existentes en otros atómicos, pero para tipos de datos no soportados como "atómicamente suma x and lo almacenado en la dirección y, y escribe el resultado en y" pero para punto flotante. Nos hemos econtrado con dos situaciones excepcionales donde: en una de ellas hemos dividido una sección crítica es multiples secciones de una única dirección: en la otra hemos conseguido, usando un constructo dentro de otro constructo, implementar una sección crítica de dos direcciones usando atómicos de dirección única. Sin embargo, las secciones críticas no lo son todo, existen otras primitivas de sincronización, como las barreras, las cuales también hemos reemplazado con alternativas que usan instrucciones atómicas de dirección única para reducir la sobrecarga de dicha primitiva. Esta sobrecarga era especialmente importante, debido a que en procesadores modernos, la cantidad de trabajo a realizar entre barrera y barrera es tan pequeño, que en algunas aplicaciones el tiempo de ejecución estaba completamente dominado por esperar a otros hilos.

Debido a las grandes limitaciones de las instrucciones atómicas de unica dirección, los atómicos de multiple dirección han sido el deseo de los desarrolladores durante muchos años. Este tipo de instrucciones permitiría implementar secciones críticas más complejas con los misma eficiencia que las instrucciones atómicas de dirección única, recordemos que las instrucciones atómicas son la manera más eficiente de realizar una actualización en una dirección de manera atómica respecto al resto the hilos de la aplicación. Sin embargo, realizar esto no es tarea sencilla. Siempre que queramos bloquear multiples direcciones de memoria hay que tener un cuidado extremo con no caer en puntos muertos donde la ejecución no puede continuar, por ejemplo el hilo 1 tiene bloqueado "x", y quiere bloquear "y", mientras el hilo 2 tiene bloqueado "y" y quiere bloquear "x". Para solucionar esto, la solución más sencilla es usar un orden global que todos sigan: Para bloquar "x" e "y", primero hay que bloquear "x" y luego "y". Esta solución funciona perfectamente en software, donde los recursos se asumen que son suficientes (sino ilimitados). Sin embargo, las instrucciones atómicas suelen implementar sus bloqueos a nivel de caché, una estructura física con unos recursos finitos y bien restringidos.

¿Como podemos implementar instrucciones atómicas de multiple dirección si tenemos recursos limitados? La respuesta que proponemos es: teniendo en cuenta esas limitaciones a la hora de ordenar las direcciones a bloquear. Siguiendo una serie de pasos muy especificos a la hora de realizar un bloqueo, y usando el orden lexicografico de las direcciones teniendo en cuenta el tamaño de la caché privada, hemos conseguido bloquear hasta 4 direcciones simultaneamente. Usando este método, hemos implementado instrucciones atómicas de multiple dirección de distinto tipo, entre ellos el conocido compare-andswap (comparar e intercambiar).

A pesar del gran paso de las instrucciones atómicas de multiple dirección, realizar algoritmos complejos con ellos sigue siendo un reto importante. Uno

de los mayores limitantes, además del número de direcciones, es la mutabilidad de las direcciones usadas. Las instrucciones atómicas, de unica o multiple dirección, requieren que las direcciones de memoria a bloquear se conozcan de ante mano, no sean mutables. Una sección crítica no es mutable si al ejecutarla multiples veces con los mismos registros del procesador, las direcciones accedidas, tanto en lectura como en escritura, son siempre las mismas. O dicho de otra manera, las direcciones de memoria no dependen de otras direcciones de memoria.

Sería mucho más sencillo si el propio hardware fuera capaz de encontrar esas direcciones, determinar la mutabilidad de la sección crítica, y realizar el bloqueo en el orden correcto sin requerir que el programador planifique la sección crítica, y por tanto solo marcando el inicio y fin de la misma.

Los dos mecanismos que alivian a los programadores de definir el tipo de bloqueo a realizar, y dejando esa tarea al propio hardware son memoria transaccional por hardware y la elisión especulativa de bloqueos. Ambas propuestas consiguen lo que se proponen, el programador solo determina las regiones de código y el hardware se encarga de intentar ejecutarlas de la manera más eficiente que sea posible. Sin embargo, ninguna de las propuestas tiene garantía de progreso, eso quiere decir que pueden fallar y tener que reintentar si se rompe la atomicidad. En ambas situaciones, la solución más empleada es un camino de ejecución altenativo que adquiere un bloque (o cerrojo) que fuerza la atomicidad, a costa del rendimiento.

Pero, ¿y si pudiesemos aprovechar esos reintentos y bloquear las direcciones de memoria necesarias para garantizar que se complete la ejecución de manera satisfactoria sin posibilidad de conflictos? cleAR usa esa primera ejecución para analizar la sección crítica, obtener todas las direcciones de memoria, e incluso analizar las dependencias, para seleccionar el método de ejecución óptimo para limitar el número de reintentos necesarios a 1. Una vez la sección crítica está en ejecución, cleAR relaja el mecanismo de prevención de conflictos para poder obtener toda la información que sea posible de la primera ejecución. Si una vez terminada, la ejecución termina con un conflicto, cleAR elige entre las tres siguientes opciones: 1) bloquear todas las direcciones y realizar una ejecución no especulativa; 2) bloquear parte de las direcciones y realizar una ejecución especulativa; y 3) no bloquear nada y continuar con el mecanismo base. En el caso de seleccionar la opción 1, el número de reintentos está limitado a 1, y no hay más posibilidad de conflictos. Sin embargo, si la sección crítica no cumple con todos los requerimientos para la opción 1, aún así podemos aumentar las posibilidades de progreso bloqueando aquellas direcciones que sean propensas a conflictos (opción 2). Como última opción, cleAR delegará en el mecanismo especulativo que se esté usando para manejar aquellas secciones críticas a las que no sea capaz de aplicar ninguno de los mecanismos anteriores.

En nuestro primer paso, Splash-4, hemos conseguido reducir el tiempo de ejecución al usar 64-cores en un 50%, manteniendo en todo momento la es-

tructura y algoritmos originales. En el segundo objectivo (MADs), las nuevas instrucciones atomicas implementadas, reducen un 80% el tiempo de ejecución al compararse con el mecanismo de locks clásico, y un 60% al usar una tecnica de memoria transacional similar a intel TSX, añadiendo solo 68 bytes por core. Por último, cleAR, es capaz de limitar la cantidad de rejecuciones de las secciones criticas ejecutadas bajo métodos especulativos, aumentando en un 35% la cantidad de secciones que se completan en el primer reintento, y reduciendo del 37% al 15% la cantidad de secciones que requieren llegar al fallback. Todo esto mejorando el tiempo de ejecución en un 35% contra una implementación tipo Intel TSX y un 23% contra PowerTM.

#### 4. Introduction

Processors' manufacturers found that increasing the performance of a core was no longer an easy task. While single-core performance is still on manufacturers' focus, most of them spend a lot of resources adding multiple cores on a processor chip (CMP or Chip-Multi-Processor). Compared to the small performance gains by improving a core, adding more cores allows continuing to show attractive performance improvements on each chip generation. CMPs, because of their huge performance, have established Symmetric Multi-Processing (SMP) as today's standard for high-performance computing. SMP exploits the concept of having multiple identical cores connected to the same main memory and devices. Ideally, an application that uses all the available cores would be able to increase the performance by a factor of the number of cores used. However, most applications require arbitration where the threads running on each core require synchronization, that is, sharing data or waiting for others to catch up.

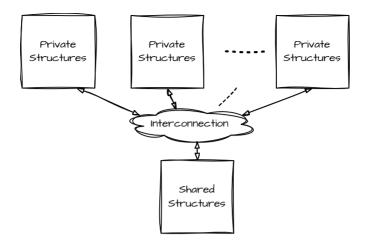

With the rapid performance increase of the cores, a huge latency breach was established with the memory. This potential bottleneck forced manufacturers to integrate local caches on each core to reduce the cost of accessing memory by keeping local copies of data blocks that will be reused by the core without having to access memory again. As the execution progresses, potential stale copies may appear, leading to inconsistencies of the same address accessed by different cores returning different values. The cache coherence protocol oversees orchestrating permissions, by giving or revoking them on each cache, to keep the data coherent between cores.

One simple solution, to keep the coherence of the data, is to notify all the caches on each operation performed (snooping). Snooping protocols, while easier to implement, induce a huge penalty that prevents the inclusion of more cores per chip, leading to their replacement with more complex, directory-based cache coherence models. The directory is a structure shared by all cores that map on which cache is each cache block, allowing to revoke or grant permissions with limited communication to the nodes that are needed. Despite the directory taking care of the cacheline orchestration, data races are an issue. Multiple threads may try to read the same data to later do an update (Shared Memory Model). Depending on the specific application and the runtime order of the threads, the result will vary.

For example, in a system with two threads that try to perform an addition on a shared memory location (x): a = load x; a = a + 1; write a in x; x initially holds the value 125. Thread 1 reads x (125) and saves the value in its local memory a, then thread 2 reads  $\times$  (125) and also saves the values in its local memory b<sup>1</sup>. The execution continues, thread 1 and thread 2 perform the additions (1: a = 126 = 125 + 1, 2: b = 126 = 125 + 1). When storing the result, thread 1 will invalidate the cacheline in thread 2, and then write (overwriting 125 with 126). Thread 2 will follow by doing the invalidation and storing the data (overwriting 126 with 126). At the start, we were expecting that with two threads increasing the value to 125, the result would be 127, but instead, in this execution, it is 126.

This scenario shows the need for a mechanism that elides threads from reading or writing when synchronization is required. Atomicity is the property that is not conservated here. In the previous example, one of the threads should wait until the other one has finished reading, adding, and writing the result. Waiting means that the program could run slower as some of the threads are waiting for others to reach a certain point, so programmers should minimize the amount of synchronization points to increase the concurrency and potentially the performance of the application.

To fix the scenario, the section of the code that reads, modifies, and writes back the data needs to be encapsulated into a critical section. Critical sections guarantee that the code is executed, or appears to be executed, isolated from the rest of the system. That is, no other core can read the intermediate state of the data nor write to it. To encapsulate the code, a lock can be set up to prevent others from executing that part of the code at the same time. The previous example can be modified as: lock; a = load x; a = a + 1; write a in x; unlock. However, while this solution works, for simple scenarios with only one variable, there is a much better approach, atomic instructions. Again, the previous example can be modified as: atomic\_fetch\_and\_increment x;. Being hardware instructions, they are much faster than locks and can be implemented in clever ways. For example, a common atomic instruction implementation is by locking the cacheline that the data belongs, preventing other cores from reading or writing to it without/minor modifications to the core or the coherence protocol.

#### 4.1 Opportunities

During the research and development of a new system, a comparison line needs to be drawn to evaluate how the proposed changes affect performance, energy consumption, or any of the other metrics of interest that are being looked to be improved. The standard current solution is the use of benchmark suites. Benchmark suites are a collection of applications and inputs that try to evaluate how a specific system would perform in a real scenario.

<sup>&</sup>lt;sup>1</sup>Note that to read the value thread 2 does not need to invalidate or send any message to thread 1.

The main issue is how old these benchmark suites are. From the most used ones (SPLASH [46, 52, 44], SPEC [47], PARSEC [53], STAMP [38], ...) are crafted over 20 years ago. Some of them try to keep up and continue receiving updates (like SPEC). Systems, compilers, programmers; all of them change over time, and quite quickly something that was thought to be the best solution to a problem, now becomes the worst. An example of this was the algorithm to exchange values between two variables. An algorithm called xor\_swap was used in the past, but with more clever compilers and with new instructions (xchg) the xor\_swap is even worse than using a third variable to perform the swap. Benchmark suites cannot keep up with these trends and always target the most recent solutions. Despite the issue that a solution can be better on one platform and worse on another.

One of the most misrepresented capabilities in benchmarks is the synchronization of parallel programs. Not all parallel programs are "embarrassingly parallel" [24], a lot of applications require some kind of orchestration between their work units. These points of synchronization are commonly known as *critical sections/critical regions/atomic regions*. Depending on the specific characteristics of the required kind of synchronization, different solutions may be applied. 1) Small critical regions that modify a limited set of addresses are "fine-grain". They tend to be quite efficient, due to their small size, but they become a real challenge to be developed. 2) Big critical regions with large sets of addresses are "coarse-grain". By default, they are quite easy to use, even automated in some cases, but with the cost of performance.

Over 10 years ago, the two main developing languages in the world, C and C++, introduced atomic instructions into their standard [28, 29]. Atomic instructions have been demonstrated to be the most efficient way of updating a variable atomically, and they started to be available in any platform, with some minor differences [27, 26, 5, 51, 23]. From their introduction in the programming standard, they were no longer limited to be used only in libraries or in operating system operations (syscall) to manage atomicity, they can be used by mainstream developers.

"Fine-grain" critical sections require a deep understanding of the data dependency between the different threads in the system. By carefully thinking about the problem that is being solved, and with the use of the blazing new standardized atomic instructions, "fine-grain" critical sections can be implemented. However, they can operate on a single-address. For simple scenarios, atomic instructions directly replace critical sections completely. But, for the complex ones, some programmers have developed tricks to implement them with these restrictions, but most developers just prefer to avoid that hustle and just use mutex lock instead.

Due to its easiness of development and being less error-prone, "coarsegrain" critical regions are used more often. Research and industry have tried to develop solutions that make "coarse-grain" critical regions to improve performance. Speculative Lock Elision (SLE) and Hardware Transactional Memory (HTM) are the main two approaches to this problem. However, they introduce a lot more challenges and hardware complexity which shows doubts if they are a good solution or not. Both approaches execute speculatively until a conflict (violation of the atomicity) is found, introducing the concept of retries. First, the waste of time and energy executing speculatively and then reverting the changes hoping that in the next retry, there is no conflict. In many cases, the amount of time required, retrying, to complete the section goes beyond the time spent if the section was serialized with traditional mutexes. Second, the pollution of structures and predictors. Depending on the implementation of the speculative execution and the recovery mechanism, after a retry, certain structures may not be restored, such as the branch predictor, the return-addressstack, and even low cache levels. In certain cases, this "pollution" helps the section to be executed correctly in the next retry [45], but if the execution path changes or the section is retried multiple times, the accuracy of these, performance-critical, structures may decline.

#### 4.2 Contributions

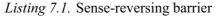

**Contribution 1 (Splash-4):** We propose an updated version of the Splash benchmark suite that manages to exploit the hardware synchronization capabilities using current up-to-date synchronization instructions. This new version introduces: 1) a different barrier synchronization primitive optimized for short waits, and 2) lock-free alternative versions of the majority of the critical sections using atomic instructions and lock-free constructs. Splash-4, executed about 50% faster in real hardware, allows the hardware designers to unveil the real causes that prevent the applications from scaling even more in contemporary.

Paper ①: Eduardo José Gómez-Hernández, Juan M. Cebrian, Stefanos Kaxiras, Alberto Ros, "Splash-4: A Modern Benchmark Suite with Lock-Free Constructs". 2022 IEEE International Symposium on Workload Characterization (IISWC 2022)

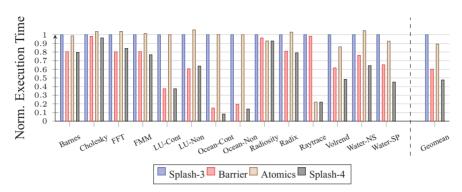

**Contribution 2 (Multi-Address Atomics):** we propose a new set of operations, and a deadlock-free locking methodology, that can perform atomic updates on multiple addresses relying solely on the coherence protocol and a predefined locking order. In contrast to speculative methodologies, this new set of operations follows the idea of atomic instructions, being non-speculative, therefore not requiring undoing work. Each cacheline required is locked with no extra communication with any other core, just the normal coherence protocol messages. Then the operation is executed atomically, and when completed, the cachelines are unlocked allowing other cores to read and write to/from them. This methodology allows us to implement Multi-Compare\_And\_Swap and Multi-Atomic\_Fetch\_And\_Add, among many others, simplifying the development of these critical sections and increasing their performance in highcontended scenarios.

Paper III: Eduardo José Gómez-Hernández, Juan M. Cebrian, Rubén Titos-Gil, Stefanos Kaxiras, Alberto Ros, "Efficient, Distributed, and Non-Speculative Multi-Address Atomic Operations". 54th Annual IEEE/ACM International Symposium on Microarchitecture (MICRO-54)

Contribution 3 (Cache Locking of Atomic Regions): We propose a technique that bounds the number of retries required to complete a coarse-grain critical region while keeping the concurrency of the execution. Instead of just executing speculatively, the structure, addresses, and dependencies of the critical section can be gathered during the retries. Therefore, using this information, a non-deadlocking order can be established to concurrently execute the section without speculation by locking the data at the cache level. We noticed that most of the time, in a critical section that is retried with the speculative solutions, the address set where it performs its operations is the same as during the first retry. Therefore, by locking that set of addresses, and preventing external access, we can guarantee that the section will be complete without having to retry more times. We go one step further, by completely disabling the speculative method and executing non-speculative if the address set is immutable, that is, the address set cannot be changed between retries. This can be seen as converting the critical section into an atomic after the first failed retry.

Paper (III): Eduardo José Gómez-Hernández, Juan M. Cebrian, Stefanos Kaxiras, Alberto Ros, "Bounding Speculative Execution of Atomic Regions to a Single Retry". International Conference on Architectural Support for Programming Languages and Operating Systems 2024 (ASPLOS 2024)

Figure 4.1 shows a summary of the contributions of the thesis. Contribution 1 solves 1-address immutable critical sections in a non-speculative way by using the atomic instructions available in current architectures. Contribution 2 solves up to 4-addresses immutable critical sections with the use of our new multi-address atomic instructions. Contribution 3 solves any size immutable and likely-immutable critical sections by analyzing the section in the first speculative execution and converting it into its non-speculative version. Future research is open to tackle mutable critical sections.

|                              | Atomic<br>instructions               | l-address immutable<br>critical sections                        | <ul> <li>ISPLASH-4:</li> <li>An update on the SPLASH<br/>Benchmark Suite focus<br/>on synchronization</li> </ul>                           |